Integrated Circuit Image Gallery

Sun UltraSPARC Microprocessor

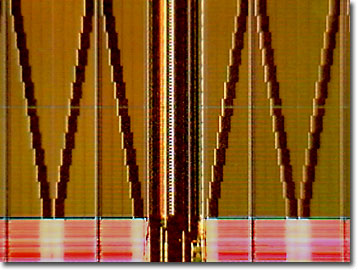

The Sun Microsystems UltraSPARC is a 64-bit superscalar processor released in late 1995 with help from Texas Instruments, following the widely successful earlier SPARC (Scalable Processor ARChitecture) designs. Being a scalable chip, as the silicon semiconductor technology improves, the design rules may be tightened, resulting in a more compact layout that takes advantage of innovations without a total redesign of the architecture.

View a low magnification image of the UltraSPARC processor.

View a medium magnification image of the UltraSPARC processor.

The Sun UltraSPARC can issue up to four simultaneous instructions to any of nine units: two integer units, two of five floating-point/graphics units (add, add and multiply, divide, and square root), and two load/store units. Sun added a block move instruction to the UltraSPARC, which bypasses the caches to avoid disrupting stored instructions and data. The Sun UltraSPARC I and II were architecturally the same, but varied in their fabrication technology. The UltraSPARC II features clock speeds ranging from 300 to 480 MHz, and is based on Sun's 0.25-micron semiconductor linewidth process.

The UltraSPARC III concentrates on improved data and instruction bandwidth, instead of addressing the need for in-order execution of instructions. The processor is also able to dispatch six instructions, rather than four, to the functional units in a fourteen-stage pipeline. Equipped with a scalable clock speed between 600 MHz and 750 MHz (for multi-processing), the UltraSPARC III is based on Sun's improved 0.18-micron technology.

The specialized pixel operations (Visual Instruction Set or VIS) of the UltraSPARC can operate in parallel on 8, 16, or 32-bit integer values packed into a 64-bit floating-point register. More advanced than other competing graphics instruction sets, such as the Intel MMX instructions, Hewlett-Packard PA-RISC MAX, and Motorola 88110 graphics extensions, VIS also features dimensional conversion, edge processing, pattern matching, and pixel distance calculations for MPEG encoders.

Contributing Authors

Omar Alvarado, Thomas J. Fellers and Michael W. Davidson - National High Magnetic Field Laboratory, 1800 East Paul Dirac Dr., The Florida State University, Tallahassee, Florida, 32310.

BACK TO THE INTEGRATED CIRCUIT IMAGE GALLERY

BACK TO THE DIGITAL IMAGE GALLERIES

Questions or comments? Send us an email.

© 1995-2025 by Michael W. Davidson and The Florida State University. All Rights Reserved. No images, graphics, software, scripts, or applets may be reproduced or used in any manner without permission from the copyright holders. Use of this website means you agree to all of the Legal Terms and Conditions set forth by the owners.

This website is maintained by our

Graphics & Web Programming Team

in collaboration with Optical Microscopy at the

National High Magnetic Field Laboratory.

Last Modification Friday, Nov 13, 2015 at 02:19 PM

Access Count Since September 17, 2002: 7703

Visit the website of our partner in introductory microscopy education:

|

|