Integrated Circuit Image Gallery

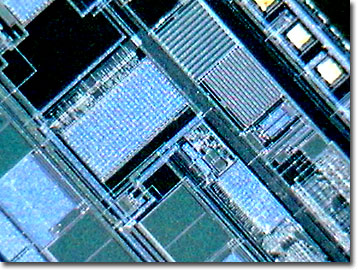

PowerPC 602 Microprocessor

The IBM/Motorola PowerPC 602 microprocessor, featuring an initial clock speed of 66 MHz, was a follow-up to the 1994 PowerPC 601. Released in February 1995 by an unusual consortium created by Apple, IBM, and Motorola, the PowerPC 602 microprocessor was designed as a low-power implementation of the reduced instruction set computer (RISC) specification for advanced consumer electronics, including handheld computers.

View a low magnification image of the PowerPC 602 processor.

Although it was designed for use in "advanced" (1995 timeline) home entertainment and educational devices having audiovisual, multimedia, and complex graphics requirements, by today's standards, the PowerPC 602 would not even come close to meeting those needs. A majority of the 602 microprocessors were utilized in notebook computers and for advanced game controllers.

The PowerPC 602 microprocessor was capable of issuing one instruction per clock cycle divided into four independent execution units. The low-power design of 3.3 volts with three power-saving modes ("doze," "nap," and "sleep") was well suited for applications involving portable electronic devices requiring conservation of battery power. Another advancement by Motorola was the application of dynamic power management to selectively activate functional units as they were needed. These services were implemented by allowing unused functional units to automatically enter a low-power state without affecting the processor performance, software execution, or external hardware. At its full operational maximum power of 1.2 watts, this chip runs at a clock speed of 66 MHz. The die size was reduced from 120 square millimeters in the 601 model to 50 square millimeters in 602 processors, and the number of transistors expanded from 1 million to 2.8 million. Although they could emulate DOS via software, the PowerPC 602 and 601 chips were not code compatible with processors that adopted the Intel architecture.

Contributing Authors

Omar Alvarado, Thomas J. Fellers and Michael W. Davidson - National High Magnetic Field Laboratory, 1800 East Paul Dirac Dr., The Florida State University, Tallahassee, Florida, 32310.

BACK TO THE INTEGRATED CIRCUIT IMAGE GALLERY

BACK TO THE DIGITAL IMAGE GALLERIES

Questions or comments? Send us an email.

© 1995-2025 by Michael W. Davidson and The Florida State University. All Rights Reserved. No images, graphics, software, scripts, or applets may be reproduced or used in any manner without permission from the copyright holders. Use of this website means you agree to all of the Legal Terms and Conditions set forth by the owners.

This website is maintained by our

Graphics & Web Programming Team

in collaboration with Optical Microscopy at the

National High Magnetic Field Laboratory.

Last Modification Friday, Nov 13, 2015 at 02:19 PM

Access Count Since September 17, 2002: 8534

Visit the website of our partner in introductory microscopy education:

|

|