Integrated Circuit Image Gallery

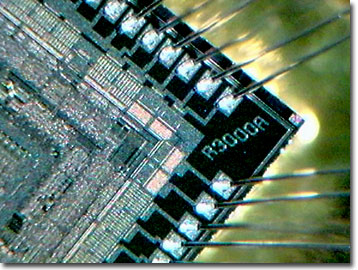

MIPS R3000 Microprocessor

In 1988, following their revolutionary R2000, MIPS Technologies Inc. released the R3000 reduced instruction set computing (RISC) microprocessor with improved cache control. Featuring 110,000 transistors fabricated by applying 1.2 micron linewidth process techniques, the microprocessor operated at a clock speed of 20 MHz with a peak power dissipation of 4.0 watts.

View a high magnification image of the MIPS R3000 processor.

As a 100 percent compatible redesign of the R2000, the R3000 microprocessor was still a 32-bit chip with a separate floating-point unit (FPU) co-processor, but clocked at a higher frequency. The 1992 version of the MIPS R3000 processor was a process shrink that featured 125,000 transistors on a 72-square millimeter die. Having a density of 1,736 transistors per square millimeter of silicon, this processor operated at a clock speed of 33 MHz. The R3000A version, basically an R2000 processor coupled to an R3010 floating-point unit, featured a 64-Kbyte cache memory and was ramped up to a 40 MHz clock speed, all integrated onto the same chip.

Reincarnated in May 1999 as the MIPS32 4Kc embedded processor core, the ubiquitous R3000 microprocessor was miniaturized to fit onto a 3-square-millimeter die utilizing a 0.25 micron linewidth process. Currently available as either synthesizable soft cores or optimized hard cores, this embedded chip is compatible with a wide range of processes and manufacturing flows. The embedded chip delivers approximately 600 million instructions per second (MIPS) per watt of consumed power, including the cache operation. Code named Jade, this 32-bit RISC processor core is optimized for low-power, battery-operated systems and for running fully compatible codes with R3000 instructions at a 200 MHz clock speed while only consuming two milliwatts per MHz.

Contributing Authors

Omar Alvarado, Thomas J. Fellers and Michael W. Davidson - National High Magnetic Field Laboratory, 1800 East Paul Dirac Dr., The Florida State University, Tallahassee, Florida, 32310.

BACK TO THE INTEGRATED CIRCUIT IMAGE GALLERY

BACK TO THE DIGITAL IMAGE GALLERIES

Questions or comments? Send us an email.

© 1995-2025 by Michael W. Davidson and The Florida State University. All Rights Reserved. No images, graphics, software, scripts, or applets may be reproduced or used in any manner without permission from the copyright holders. Use of this website means you agree to all of the Legal Terms and Conditions set forth by the owners.

This website is maintained by our

Graphics & Web Programming Team

in collaboration with Optical Microscopy at the

National High Magnetic Field Laboratory.

Last Modification Friday, Nov 13, 2015 at 02:19 PM

Access Count Since September 17, 2002: 15876

Visit the website of our partner in introductory microscopy education:

|

|